# **Towards scalable RDMA locking on a NIC**

#### **TORSTEN HOEFLER**

with support of Patrick Schmid, Maciej Besta, Salvatore di Girolamo @ SPCL presented at HP Labs, Palo Alto, CA, USA

# **NEED FOR EFFICIENT LARGE-SCALE SYNCHRONIZATION**

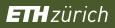

# LOCKS: CHALLENGES

# LOCKS: CHALLENGES

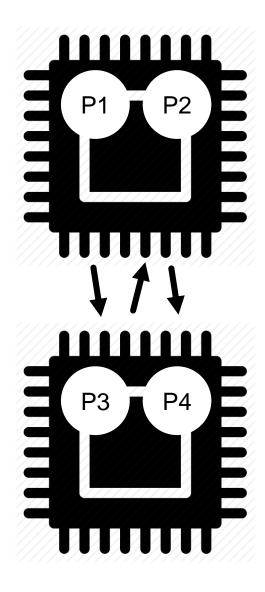

We need intra- and inter-node topologyawareness

We need to cover arbitrary topologies

# **LOCKS: CHALLENGES**

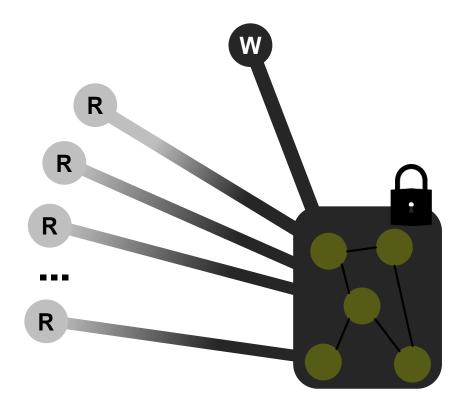

Reader

# We need to distinguish between readers and writers

Reader

Reader

We need flexible performance for both types of processes

[1] V. Venkataramani et al. Tao: How facebook serves the social graph. SIGMOD'12.

# What will we use in the design?

8

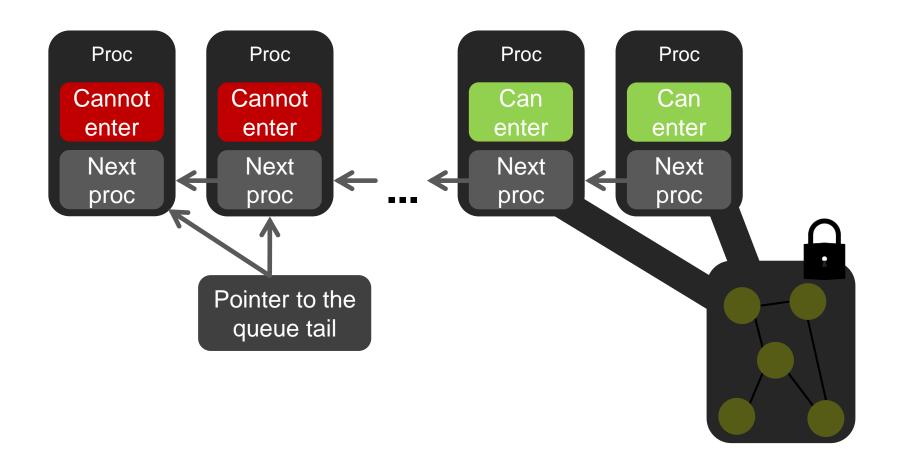

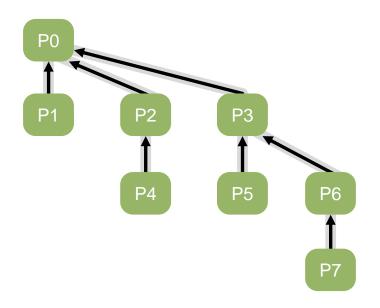

# WHAT WE WILL USE MCS Locks

# WHAT WE WILL USE Reader-Writer Locks

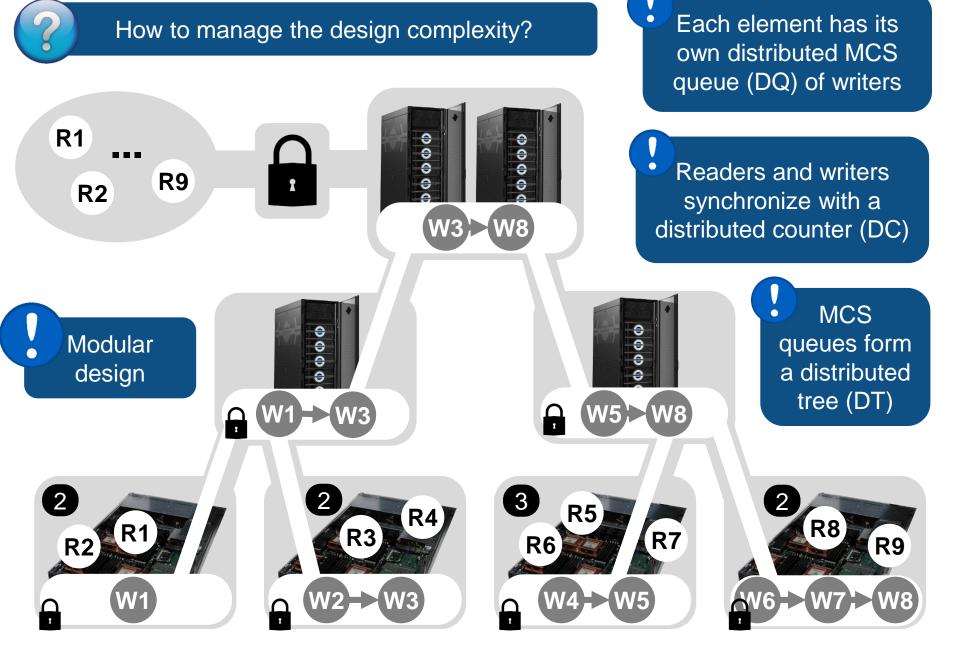

# How to manage the design complexity?

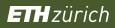

# How to ensure tunable performance?

# What mechanism to use for efficient implementation?

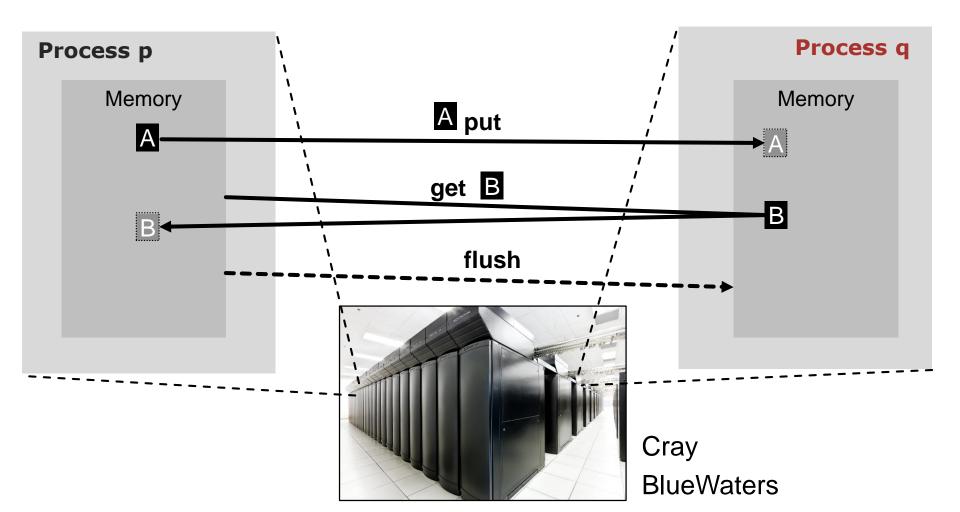

# **REMOTE MEMORY ACCESS (RMA) PROGRAMMING**

# **REMOTE MEMORY ACCESS PROGRAMMING**

Implemented in hardware in NICs in the majority of HPC networks support RDMA

# How to manage the design complexity?

# How to ensure tunable performance?

What mechanism to use for efficient implementation?

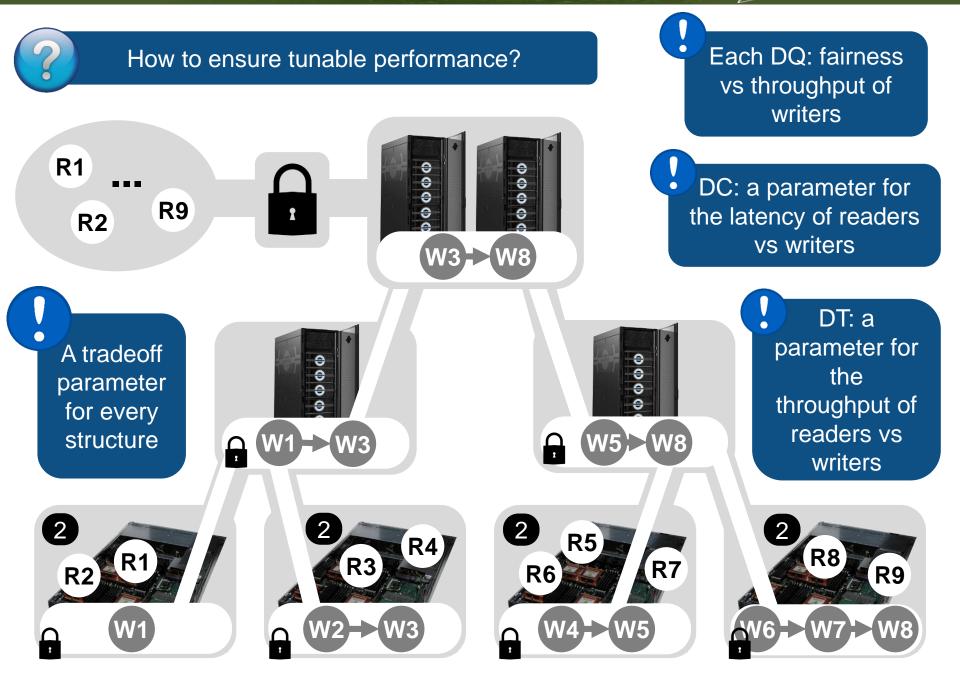

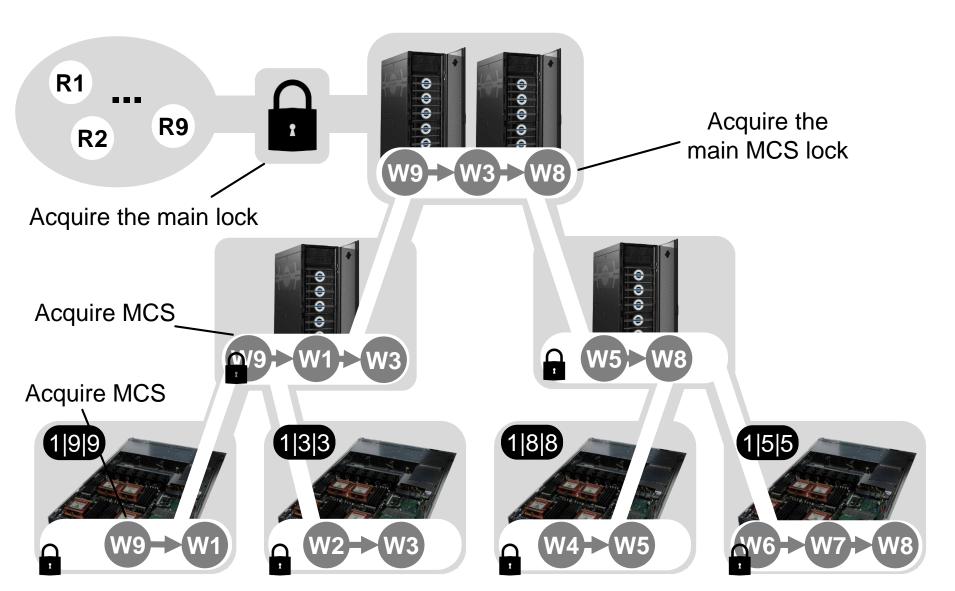

Each DQ: The

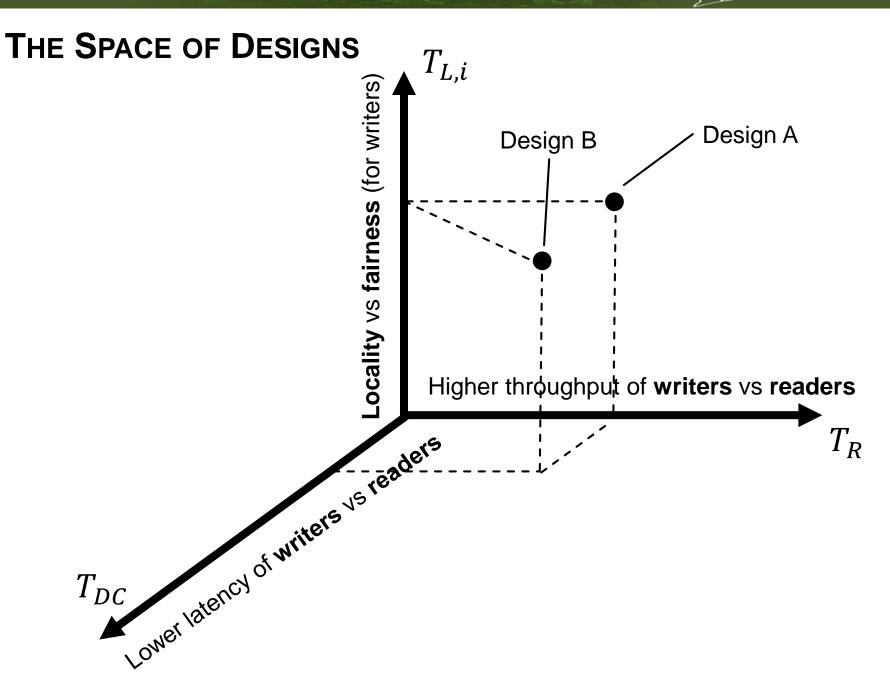

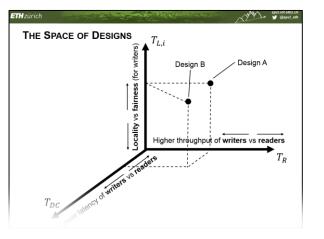

# DISTRIBUTED MCS QUEUES (DQS) Throughput vs Fairness

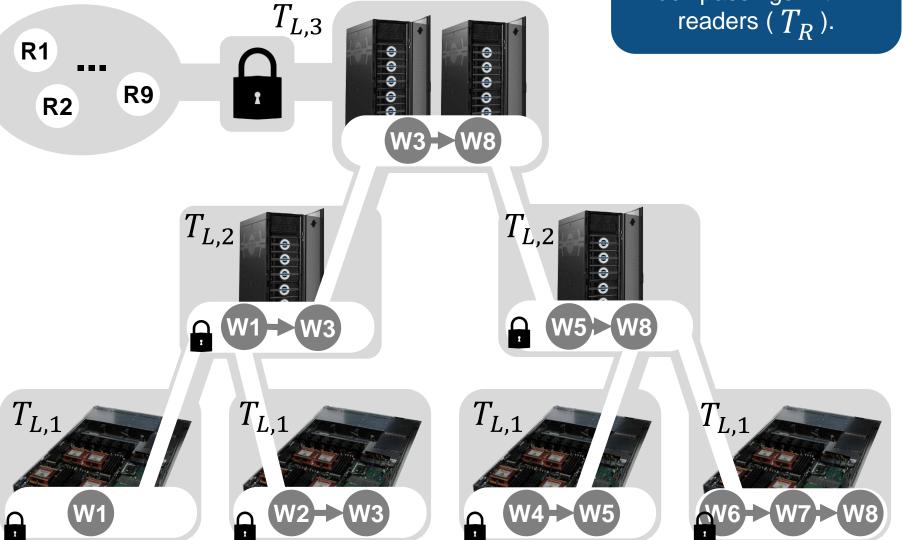

# **DISTRIBUTED TREE OF QUEUES (DT)** Throughput of readers vs writers

DT: The maximum number of consecutive lock passings within readers ( $T_R$ ).

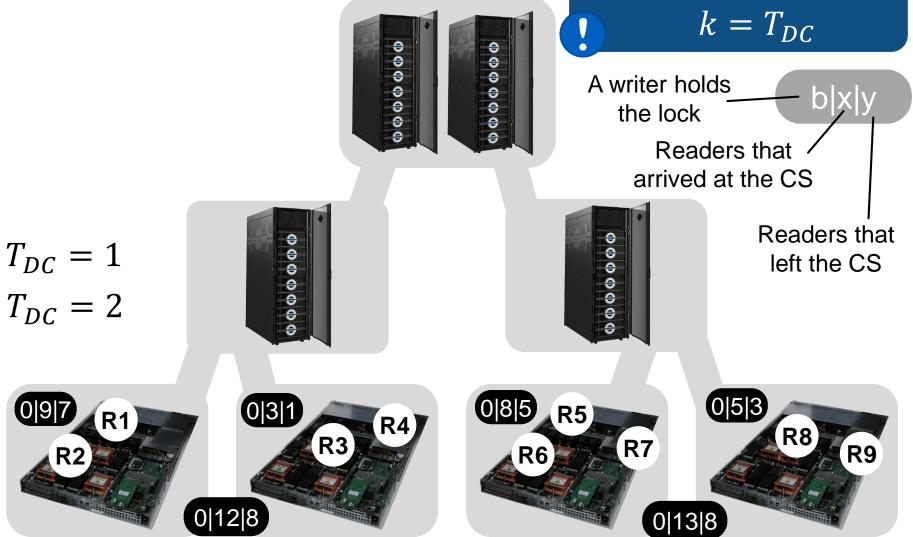

# **DISTRIBUTED COUNTER (DC)** Latency of readers vs writers

DC: every *k*th compute node hosts a partial counter, all of which constitute the DC. k - T

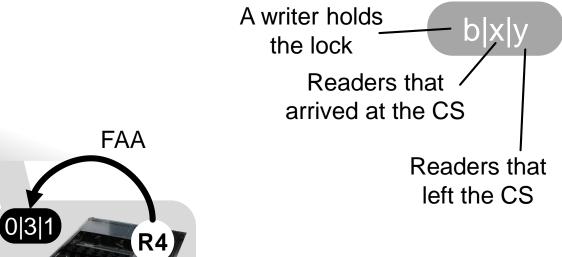

# LOCK ACQUIRE BY READERS

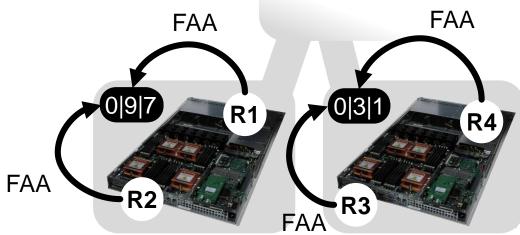

A lightweight acquire protocol for readers: only one atomic fetch-and-add (FAA) operation

# LOCK ACQUIRE BY WRITERS

#### ETHzürich

CRAY CRAY

C3

CRAY

CRAY

spcl.inf.ethz.ch

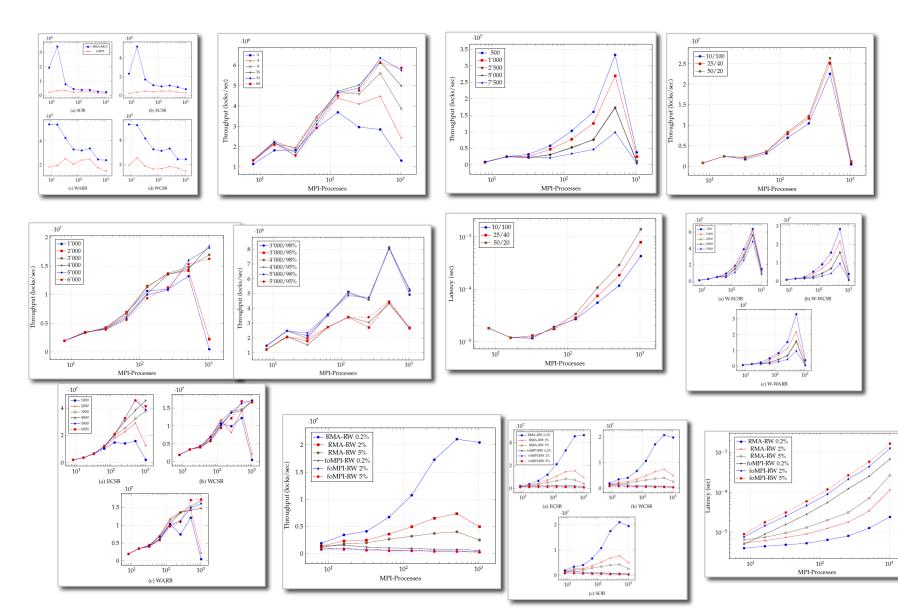

# **EVALUATION**

- CSCS Piz Daint (Cray XC30)

- 5272 compute nodes

- 8 cores per node

- 169TB memory

# EVALUATION CONSIDERED BENCHMARKS

The latency benchmark

# DHT

Distributed hashtable evaluation Throughput benchmarks:

Empty-critical-section Single-operation Wait-after-release Workload-critical-section

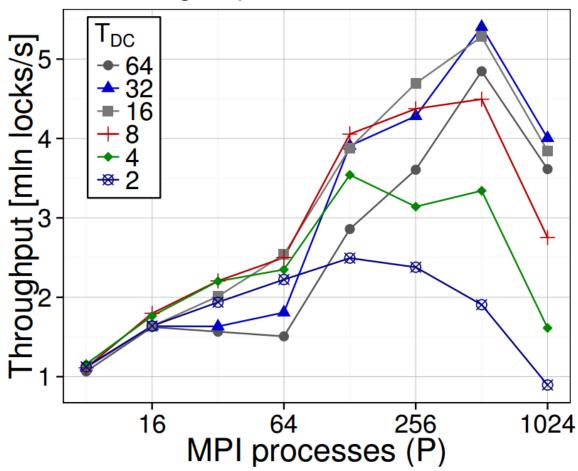

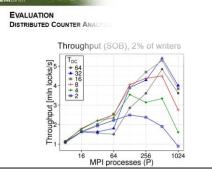

# **EVALUATION** DISTRIBUTED COUNTER ANALYSIS

Throughput, 2% writers

Single-operation benchmark

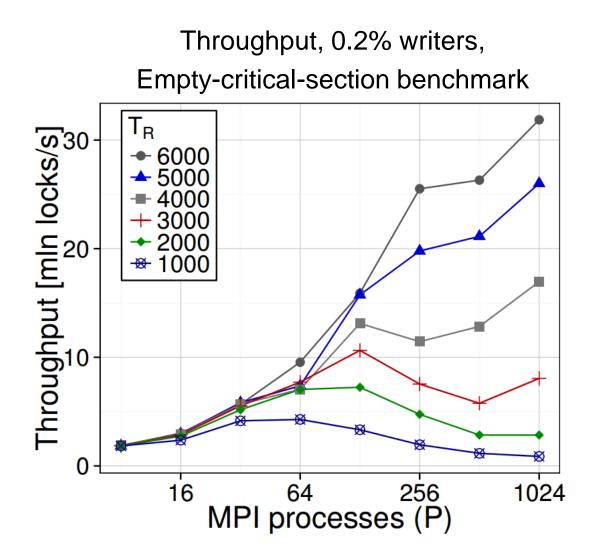

# **EVALUATION** READER THRESHOLD ANALYSIS

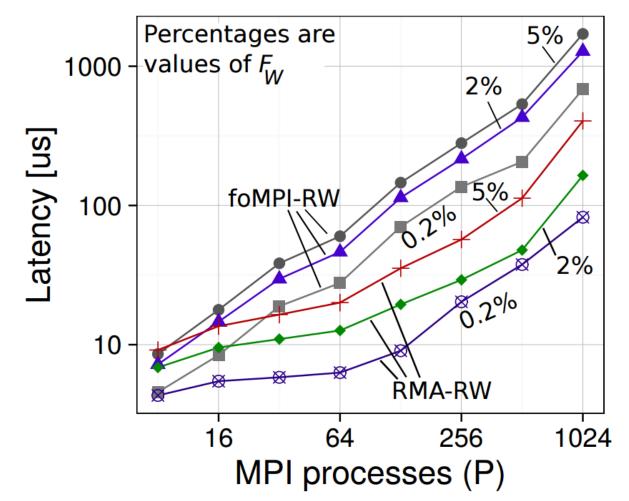

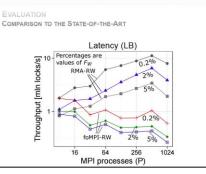

### **EVALUATION** COMPARISON TO THE STATE-OF-THE-ART

[1] R. Gerstenberger et al. Enabling Highly-scalable Remote Memory Access Programming with MPI-3 One Sided. ACM/IEEE Supercomputing 2013.

### **EVALUATION** COMPARISON TO THE STATE-OF-THE-ART

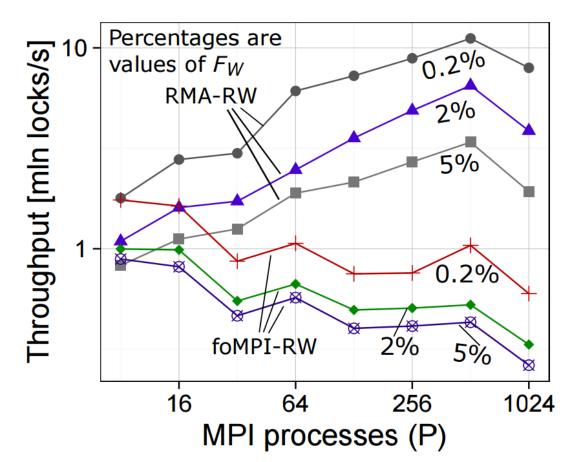

Throughput, single-operation benchmark

[1] R. Gerstenberger et al. Enabling Highly-scalable Remote Memory Access Programming with MPI-3 One Sided. ACM/IEEE Supercomputing 2013.

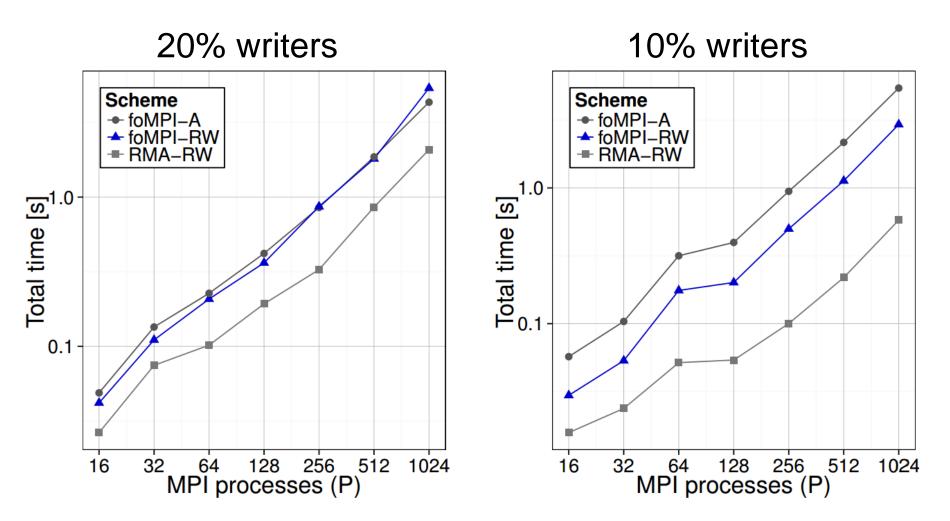

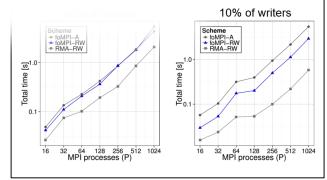

# **EVALUATION** DISTRIBUTED HASHTABLE

[1] R. Gerstenberger et al. Enabling Highly-scalable Remote Memory Access Programming with MPI-3 One Sided. ACM/IEEE Supercomputing 2013.

# **EVALUATION DISTRIBUTED HASHTABLE**

### 2% of writers

# 0% of writers

[1] R. Gerstenberger et al. Enabling Highly-scalable Remote Memory Access Programming with MPI-3 One Sided. ACM/IEEE Supercomputing 2013.

# **OTHER ANALYSES**

A COLOR

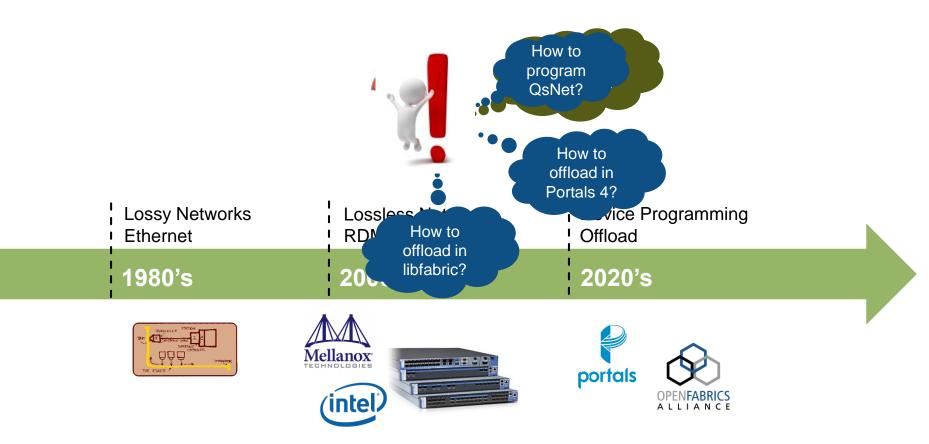

# But why stop at RDMA -- A brief history

# **Performance Model**

[1] A. Alexandrov et al. "LogGP: incorporating long messages into the LogP model—one step closer towards a realistic model for parallel computation.", Proceedings of the seventh annual ACM symposium on Parallel algorithms and architectures. ACM, 1995.

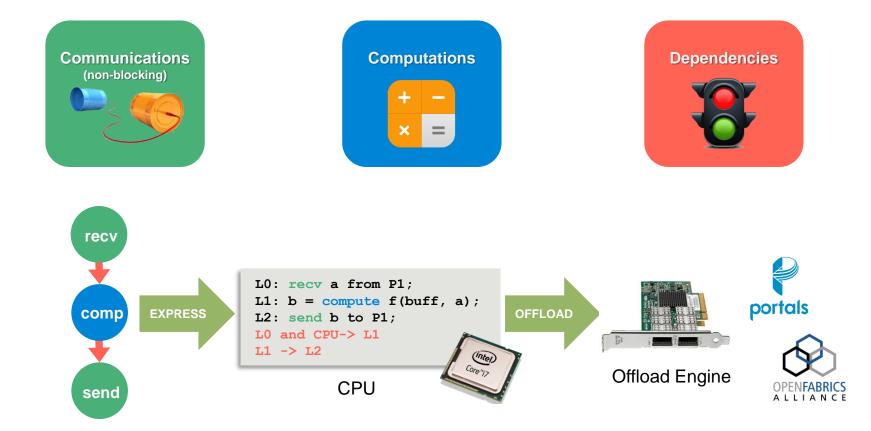

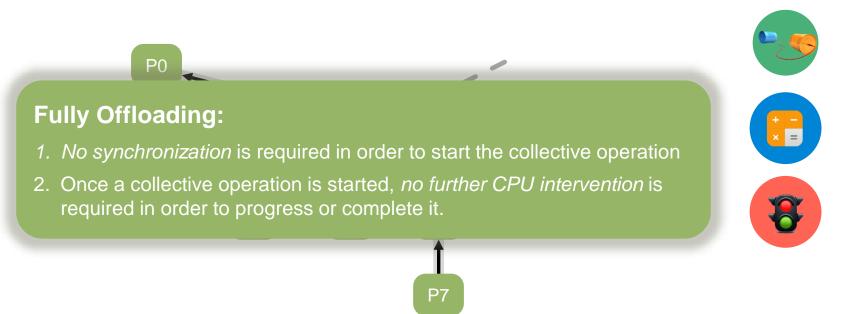

# **Fully Offloaded Collectives**

**Collective communication**: A communication that involves a group of processes **Non-blocking collective:** Once initiated the operation may progress independently of any computation or other communication at participating processes

# **Fully Offloaded Collectives**

**Collective communication**: A communication that involves a group of processes

**Non-blocking collective:** Once initiated the operation may progress independently of any computation or other communication at participating processes

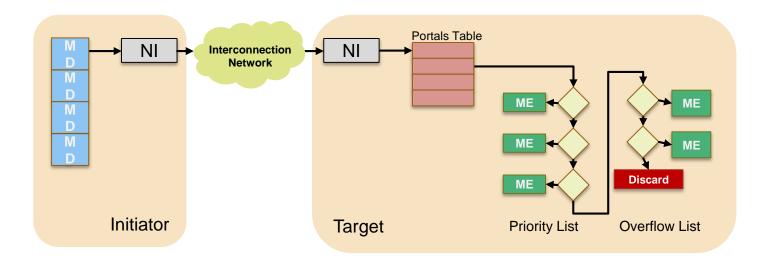

# A Case Study: Portals 4

- Based on the one-sided communication model

- Matching/Non-Matching semantics can be adopted

spcl.inf.ethz.ch Ƴ @spcl\_eth

# A Case Study: Portals 4

#### **Communication primitives**

- Put/Get operations are natively supported by Portals 4

- One-sided + matching semantic

#### **Atomic operations**

- Operands are the data specified by the MD at the initiator and by the ME at the target

- Available operators: *min, max, sum, prod, swap, and, or, …*

#### Counters

- Associated with MDs or MEs

- Count specific events (e.g., operation completion)

#### **Triggered operations**

- Put/Get/Atomic associated with a counter

- Executed when the associated counter reaches the specified threshold

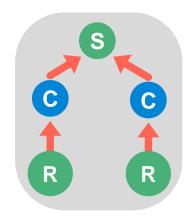

# **FFlib: An Example**

Proof of concept library implemented on top of Portals 4

```

ff_schedule_h sched = ff_schedule_create(...);

```

```

ff_op_h r1 = ff_op_create_recv(tmp + blocksize, blocksize, child1, tag);

ff op h r2 = ff op create recv(tmp + 2*blocksize, blocksize, child2, tag);

```

ff\_op\_h c1 = ff\_op\_create\_computation(rbuff, blocksize, tmp + blocksize, blocksize, operator, datatype, tag)

ff op h c2 = ff op create computation(rbuff, blocksize, tmp + 2\*blocksize, blocksize, operator, datatype, tag)

ff op h s = ff op create send(rbuff, blocksize, parent, tag)

```

ff_op_hb(r1, c1)

ff_op_hb(r2, c2)

ff_op_hb(c1, s)

ff_op_hb(c2, s)

```

ff\_schedule\_add(sched, r1)

ff\_schedule\_add(sched, r2)

ff\_schedule\_add(sched, c1)

ff\_schedule\_add(sched, c2)

ff schedule\_add(sched, s)

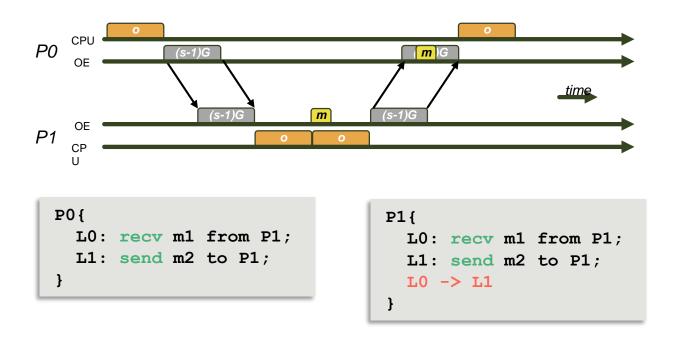

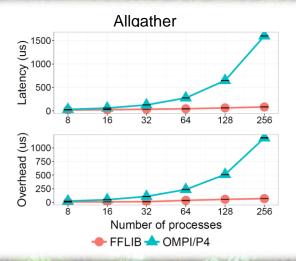

# **Experimental Results**

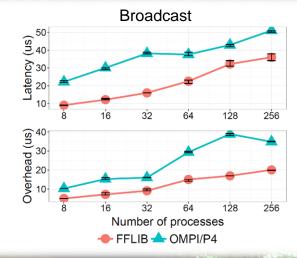

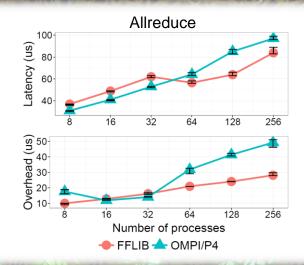

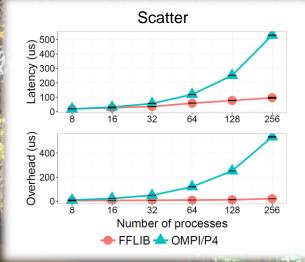

**Target machine: Curie** 5,040 nodes 2 eight-core Intel Sandy Bridge processors Full fat-tree Infiniband QDR OMPI/P4: Open MPI 1.8.4 + Portals 4 RL FFLIB: proof of concept library

# **Experimental Results: Latency/Overhead**

**Target machine: Curie** 5,040 nodes 2 eight-core Intel Sandy Bridge processors Full fat-tree Infiniband QDR OMPI/P4: Open MPI 1.8.4 + Portals 4 RL FFLIB: proof of concept library

# **Experimental Results: Latency/Overhead**

**Target machine: Curie** 5,040 nodes 2 eight-core Intel Sandy Bridge processors Full fat-tree Infiniband QDR OMPI/P4: Open MPI 1.8.4 + Portals 4 RL FFLIB: proof of concept library

# **Experimental Results: Micro-Benchmarks**

**3DFFT**

PGMRES

**Target machine: Curie** 5,040 nodes 2 eight-core Intel Sandy Bridge processors Full fat-tree Infiniband QDR OMPI/P4: Open MPI 1.8.4 + Portals 4 RL FFLIB: proof of concept library

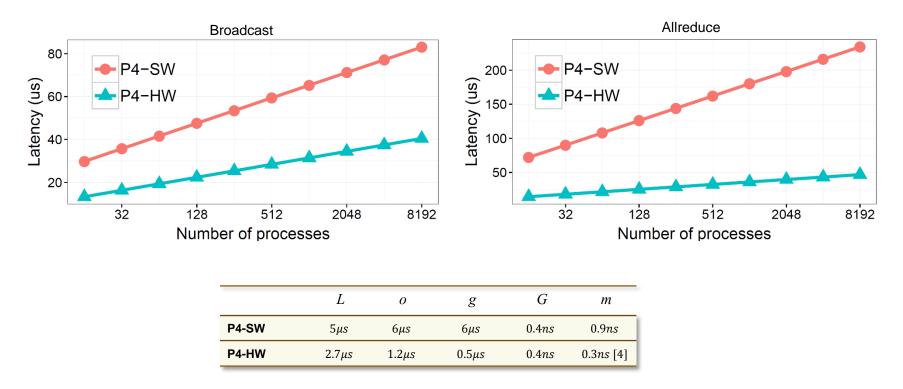

# Simulations

- Why? To study offloaded collectives at large scale

- How? Extending the LogGOPSim to simulate Portals 4 functionalities

[3] T. Hoefler, T. Schneider, A. Lumsdaine. "LogGOPSim - Simulating Large-Scale Applications in the LogGOPS Model", In Proceedings of the 19th ACM International Symposium on High Performance Distributed Computing (HPDC '10). ACM, 2010.

[4] Underwood et al., "Enabling Flexible Collective Communication Offload with Triggered Operations", IEEE 19th Annual Symposium on High Performance Interconnects (HOTI '11). IEEE, 2011.

this line the other think FFLIB-HW uses m = 0.3µ, discussed in (3) to model the incoming (2) N. Kanter, S. Batratine, A. Saranista, Lag 2018 in - Emission graph last approximation in the Lag 2018 Hours' (2) International Methods (2) International Construction in Program Spectrum).

. .

#### spcl.inf.ethz.ch ਤ 🍯 @spcl\_eth

∧\*¥\\_\_ ¥ @

# CONCLUSIONS

# Modular o

# Thank you for your attention

Improves latency and throughput over state-of-the-art

ble

les

Enables high-performance distributed hashtabled