| ETHzürich                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | spcl.inf.ethz.ch                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Our S                                                                                                                                                                          | mall Quiz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

| <ul> <li>Rec</li> <li>Virt</li> <li>Virt</li> <li>A h</li> <li>If a ove</li> <li>x86</li> <li>x86</li> <li>x86</li> <li>A vi</li> <li>Par</li> <li>A p</li> <li>Sha</li> </ul> | or false (raise hand)<br>ceiver side scaling randomizes on a per-packet basis<br>rual machines can be used to improve application perform<br>rual machines can be used to consolidate servers<br>ypervisor implements functions similar to a normal OS<br>CPU is strictly virtualizable, then OS code execution cau<br>erheads<br>b is not strictly virtualizable because some instructions fail<br>ecuted in ring 1<br>can be virtualized by binary rewriting<br>irtualized host operating system can set the hardware PT<br>ravirtualization does not require changes to the guest OS<br>age fault with shadow page tables is faster than nested p<br>age fault with writeable page tables is faster than shadow<br>adow page tables are safer than writable page tables<br>adow page tables require paravirtualization | ises nearly no<br>I when<br>BR<br>page tables |

| <ul> <li>A vi</li> <li>Par</li> <li>A p.</li> <li>A p.</li> <li>Sha</li> </ul>                                                                                                 | irtualized host operating system can set the hardware PT<br>ravirtualization does not require changes to the guest OS<br>age fault with shadow page tables is faster than nested p<br>age fault with writeable page tables is faster than shadow<br>adow page tables are safer than writable page tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bage tables                                   |

|                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |

| ETHzürich | spcl.inf.e                                                                                                                       | ethz.ch<br>cl_eth |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Relia     | bility and Availabilty                                                                                                           |                   |

| A storag  | ige system is:                                                                                                                   |                   |

|           | able if it continues to store data and can read and write it.<br>celiability: probability it will be reliable for some period of |                   |

|           | <i>ilabl</i> e if it responds to requests<br><mark>vailability</mark> : probability it is available at any given time            |                   |

|           |                                                                                                                                  |                   |

|           |                                                                                                                                  |                   |

|           |                                                                                                                                  |                   |

|           |                                                                                                                                  |                   |

|           |                                                                                                                                  |                   |

|           |                                                                                                                                  |                   |

| spcl.inf.ethz.ch |

|------------------|

|                  |

|                  |

|                  |

|                 |         | Sea                                                                                                                                                                                                         | agate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | urer's v                                       | , |

|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---|

| Persist         | ent     | Specifications                                                                                                                                                                                              | 3 <b>TB</b> <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2TB1                                           |   |

|                 |         | Model Number                                                                                                                                                                                                | ST33000651AS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ST32000641AS                                   |   |

| errors that     | at are  | Interface Options                                                                                                                                                                                           | SATA 6Gb/s NCQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SATA 6Gb/s NCQ                                 |   |

| <i>not</i> mask | ed by   | Performance                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |   |

|                 |         | Transfer Rate, Max Ext (MB/s)                                                                                                                                                                               | 600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 600                                            |   |

| coding ir       | iside , | Max Sustained Data Rate OD (MB/s)                                                                                                                                                                           | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 138                                            |   |

| the dri         | ive     | Cache (MB)                                                                                                                                                                                                  | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64                                             |   |

|                 |         | Average Latency (ms)                                                                                                                                                                                        | 4.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.16                                           |   |

|                 |         | Spindle Speed (RPM)                                                                                                                                                                                         | 7200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7200                                           |   |

|                 |         |                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                              |   |

|                 |         | Configuration/Organization                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                |   |

|                 |         | Configuration/Organization<br>Heads/Disks                                                                                                                                                                   | 10/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8/4                                            |   |

|                 |         |                                                                                                                                                                                                             | 10/5<br>512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8/4<br>512                                     |   |

|                 |         | Heads/Disks                                                                                                                                                                                                 | and the second se |                                                |   |

|                 |         | Heads/Disks<br>Bytes per Sector                                                                                                                                                                             | and the second se |                                                |   |

|                 |         | Heads/Disks<br>Bytes per Sector<br><b>Reliability/Data Integrity</b>                                                                                                                                        | 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 512                                            |   |

|                 |         | Heads/Disks<br>Bytes per Sector<br><b>Reliability/Data Integrity</b><br>Load/Unload Cycles                                                                                                                  | 512<br>300K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 512<br>300K                                    |   |

|                 |         | Heads/Disks<br>Bytes per Sector<br>Reliability/Data Integrity<br>Load/Unload Cycles<br>Nonrecoverable Read Errors per Bits Read, Ma                                                                         | 512<br>500K<br>1 per 10E14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 512<br>300K<br>1 per 10E14                     |   |

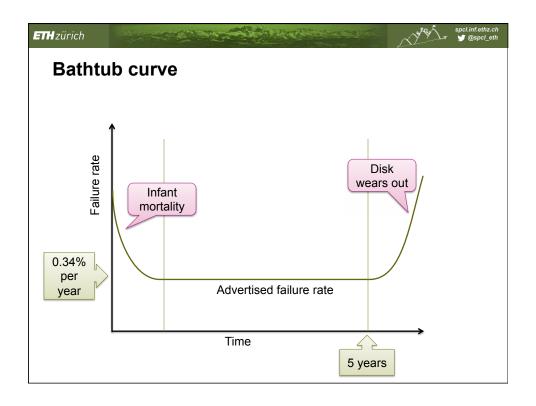

|                 |         | Heads/Disks<br>Bytes per Sector<br>Reliability/Data Integrity<br>Load/Unload Cycles<br>Nonrecoverable Read Errors per Bits Read, Ma<br>Annualized Failure Rate (AFR)                                        | 512<br>500K<br>1 per 10E14<br>0.34%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 512<br>300K<br>1 per 10E14<br>0.34%            |   |

|                 |         | Heads/Disks<br>Bytes per Sector<br>Reliability/Data Integrity<br>Load/Unload Cycles<br>Nonrecoverable Read Errors per Bits Read, Mac<br>Amunalized Failure Rate (AFR)<br>Mean Time Between Failures (hours) | 512<br>500K<br>1 per 10E14<br>0.34%<br>750,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 512<br>300K<br>1 per 10E14<br>0.34%<br>750,000 |   |

| <ul> <li>Unrecoverable read errors</li> <li>What's the chance we could read a <i>full</i> 3TB</li> </ul> |  |

|----------------------------------------------------------------------------------------------------------|--|

| <ul> <li>What's the chance we could read a <i>full</i> 3TB</li> </ul>                                    |  |

| disk without errors?                                                                                     |  |

| • For each bit:<br>$Pr(success) = 1 - 10^{-14}$                                                          |  |

| Whole disk:                                                                                              |  |

| $\Pr(success) = (1 - 10^{-14})^{8 \times 3 \times 10^{12}}$                                              |  |

| ≈ <b>0</b> . 7868                                                                                        |  |

| • Feeling lucky? Lots of assumptions:<br>Independent errors,<br>etc.                                     |  |

| ETHzürich   |                                               | and the        |                | spcl.inf.ethz.ch<br>y @spcl_eth |

|-------------|-----------------------------------------------|----------------|----------------|---------------------------------|

| Specificati | ons (from mar                                 | ufact          | urer's v       | vebsite)                        |

|             | Se                                            | agate          |                |                                 |

|             | Specifications                                | 3TB1           | 2TB1           |                                 |

|             | Model Number                                  | ST33000651AS   | ST32000641AS   |                                 |

|             | Interface Options                             | SATA 6Gb/s NCQ | SATA 6Gb/s NCQ |                                 |

|             | Performance                                   |                |                |                                 |

|             | Transfer Rate, Max Ext (MB/s)                 | 600            | 600            |                                 |

|             | Max Sustained Data Rate OD (MB/s)             | 149            | 138            |                                 |

|             | Cache (MB)                                    | 64             | 64             |                                 |

|             | Average Latency (ms)                          | 4.16           | 4.16           |                                 |

|             | Spindle Speed (RPM)                           | 7200           | 7200           |                                 |

|             | Configuration/Organization                    |                |                |                                 |

|             | Heads/Disks                                   | 10/5           | 8/4            |                                 |

|             | Bytes per Sector                              | 512            | 512            |                                 |

|             | Reliability/Data Integrity                    |                |                |                                 |

|             | Load/Unload Cycles                            | 300K           | 300K           |                                 |

|             | Nonrecoverable Read Errors per Bits Read, Max | 1 per 10E14    | 1 per 10E14    |                                 |

|             | Annualized Failure Rate (AFR)                 | 0.34%          | 0.34%          |                                 |

|             | Mean Time Between Failures (hours)            | 750,000        | 750,000        |                                 |

|             | Limited Warranty (years)                      | 5              | 5              |                                 |

|             | Power Management                              |                |                |                                 |

|             | Startun Current +12 Peak (A +10%)             | 2.0            | 2.8            |                                 |

| ETHzürich | spcl.inf.ethz.ch<br>♥ @spcl_eth                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------|

| Mean      | time to repair (MTTR)                                                                                            |

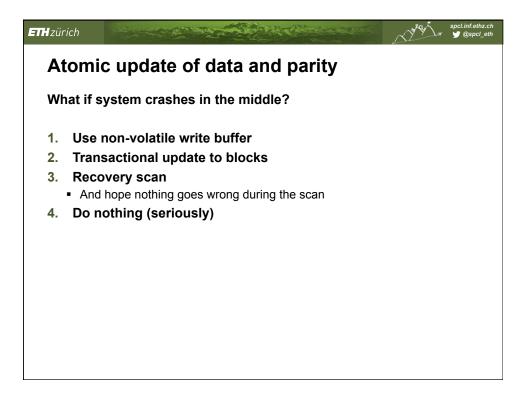

| RAID-5    | can lose data in three ways:                                                                                     |

| 1. Two    | o full disk failures (second while the first is recovering)                                                      |

| 2. Full   | disk failure and sector failure on another disk                                                                  |

| 3. Ove    | erlapping sector failures on two disks                                                                           |

|           | <b>R: Mean time to repair</b><br>pected time from disk failure to when new disk is fully rewritten, often<br>urs |

| • MTT     | DL: Mean time to data loss                                                                                       |

| ■ Ex      | pected time until 1, 2 or 3 happens                                                                              |

|           |                                                                                                                  |

|           |                                                                                                                  |

|           |                                                                                                                  |

|           |                                                                                                                  |

|           |                                                                                                                  |

| ETHzürich |            |                     |                         |                     |       |                     |                     | ß                   | Jaren -             | spcl.inf.ethz.ch<br>Ƴ @spcl_eth |

|-----------|------------|---------------------|-------------------------|---------------------|-------|---------------------|---------------------|---------------------|---------------------|---------------------------------|

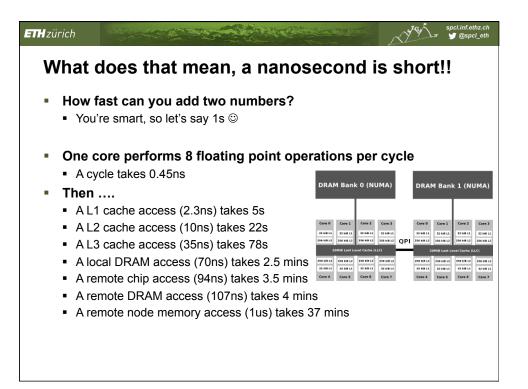

| More      | and        | more                | e cor                   | es                  | •     |                     |                     |                     |                     |                                 |

| - Like    | this dı    | ual-soc             | ket Sa                  | andy B              | ridge | syste               | m:                  |                     |                     |                                 |

|           | DRAM       | M Banl              | < 0 (NI                 | UMA)                |       | DRAI                | M Banl              | k 1 (NI             | JMA)                |                                 |

| 70 ns     |            |                     |                         |                     |       |                     |                     |                     |                     | 107                             |

|           | Core 0     | Core 1              | Core 2                  | Core 3              |       | Core 0              | Core 1              | Core 2              | Core 3              | 107 ns                          |

| 35 ns 👞   | 32 kiB L1  | 32 kiB L1           | 32 kiB L1               | 32 kiB L1           |       | 32 kiB L1           | 32 kiB L1           | 32 kiB L1           | 32 kiB L1           |                                 |

|           | 256 kiB L2 | 256 kiB L2          | 256 kiB L2              | 256 kiB L2          | QPI   | 256 kiB L2          | 256 kiB L2          | 256 kiB L2          | 256 kiB L2          | Core* 17                        |

| 10 ns     | 2          | 0MiB Last Le        | evel Cache (I           | LLC)                | 1     | 2                   | 0MiB Last Le        | evel Cache (l       | .LC)                | Core*17                         |

| 2.3ns     | 256 kiB L2 | 256 kiB L2          | 256 kiB L2<br>32 kiB L1 | 256 kiB L2          |       | 256 kiB L2          | 256 kiB L2          | 256 kiB L2          | 256 kiB L2          |                                 |

|           | Core 4     | 32 kiB L1<br>Core 5 | Core 6                  | 32 kiB L1<br>Core 7 |       | 32 kiB L1<br>Core 4 | 32 kiB L1<br>Core 5 | 32 kiB L1<br>Core 6 | 32 kiB L1<br>Core 7 |                                 |

|           |            |                     |                         | 94 ns <i>'</i>      | /     |                     | 1 us                | _                   |                     | 50.4.8 (park ) (2000)           |

|           |            |                     |                         |                     |       |                     | TUS                 |                     |                     |                                 |

| ETHzürich  |                                  |              |            | in the second | C. Sala    |              | A             | Jorge -    | spcl.inf.ethz.ch<br>Ƴ @spcl_eth |

|------------|----------------------------------|--------------|------------|---------------|------------|--------------|---------------|------------|---------------------------------|

| Non-Unifo  | Non-Uniform Memory Access (NUMA) |              |            |               |            |              |               |            |                                 |

|            |                                  |              | <b>,</b>   |               | (-         |              | -/            |            |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

| DRA        | M Bank                           | < 0 (NI      | JMA)       |               | DRAN       | M Banl       | < 1 (NI       | JMA)       |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

| Core 0     | Core 1                           | Core 2       | Core 3     |               | Core 0     | Core 1       | Core 2        | Core 3     |                                 |

| 32 kiB L1  | 32 kiB L1                        | 32 kiB L1    | 32 kiB L1  |               | 32 kiB L1  | 32 kiB L1    | 32 kiB L1     | 32 kiB L1  |                                 |

| 256 kiB L2 | 256 kiB L2                       | 256 kiB L2   | 256 kiB L2 | QPI           | 256 kiB L2 | 256 kiB L2   | 256 kiB L2    | 256 kiB L2 |                                 |

| 2          | 0MiB Last Le                     | vel Cache (l | .LC)       |               | 2          | 0MiB Last Le | evel Cache (L | .LC)       |                                 |

| 256 kiB L2 | 256 kiB L2                       | 256 kiB L2   | 256 kiB L2 |               | 256 kiB L2 | 256 kiB L2   | 256 kiB L2    | 256 kiB L2 |                                 |

| 32 kiB L1  | 32 kiB L1                        | 32 kiB L1    | 32 kiB L1  |               | 32 kiB L1  | 32 kiB L1    | 32 kiB L1     | 32 kiB L1  |                                 |

| Core 4     | Core 5                           | Core 6       | Core 7     |               | Core 4     | Core 5       | Core 6        | Core 7     |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

|            |                                  |              |            |               |            |              |               |            |                                 |

| ETHzürich                 | spcl.int.ethz.ch<br>y @spcl_eth                                                                                                                            |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

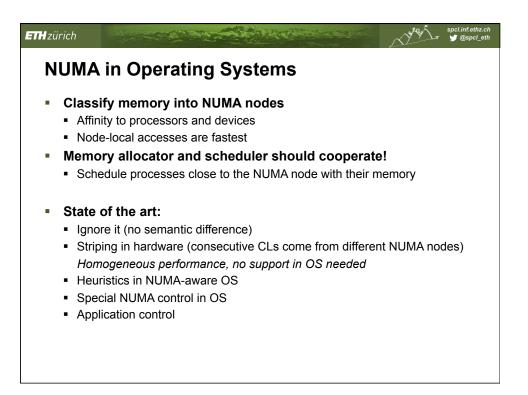

| Heuris                    | stics in NUMA-aware OS                                                                                                                                     |

| <ul> <li>Alloc</li> </ul> | <b>touch" allocation policy</b><br>cate memory in the node where the process is running<br>create big problems for parallel applications (see DPHPC class) |

| • NUMA                    | A-aware scheduling                                                                                                                                         |

| <ul> <li>Pref</li> </ul>  | er CPUs in NUMA nodes where a process has memory                                                                                                           |

| -                         | cate "hot" OS data structures                                                                                                                              |

| • One                     |                                                                                                                                                            |

| Some                      | do page striping in software                                                                                                                               |

|                           | cate pages round robin                                                                                                                                     |

| ■ Unc                     | lear benefits                                                                                                                                              |

|                           |                                                                                                                                                            |

|                           |                                                                                                                                                            |

|                           |                                                                                                                                                            |

| ETHzüric | h spcl.inf.ethz.ch<br>♥@spcl_eth |

|----------|----------------------------------|

| No       | n-local system times ©           |

| • 1      |                                  |

| RANK |                                                                             | ember 2014<br>SYSTEM                                                                                                              | CORES     | RMAX     | RPEAK<br>(TFLOP/S) | POWER<br>(KW) |                                                                                                  |

|------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|----------|--------------------|---------------|--------------------------------------------------------------------------------------------------|

| 1    | National Super<br>Computer Center in<br>Guangzhou<br>China                  | Tianhe-2 (NilkyWay-2) - TH-IVB-<br>FEP Cluster, Intel Xeon E5-2692<br>12C 2.200GHz, TH Express-2, Intel<br>Xeon Phi 31S1P<br>NUDT | 3,120,000 | 33,862.7 | 54,902.4           | 17,808        | IDC, 2009: "expects the<br>HPC technical server<br>market to grow at a<br>healthy 7% to 8% yearl |

| 2    | DOE/SC/Oak Ridge<br>National Laboratory<br>United States                    | Titan - Cray XK7, Opteron 6274<br>16C 2.200GHz, Cray Gemini<br>interconnect, NVIDIA K20x<br>Cray Inc.                             | 560,640   | 17,590.0 | 27,112.5           | 8,209         | rate to reach revenues<br>of \$13.4 billion by 2015                                              |

| 3    | DOE/NNSA/LLNL<br>United States                                              | Sequoia - BlueGene/Q, Power BQC<br>16C 1.60 GHz, Custom<br>IBM                                                                    | 1,572,864 | 17,173.2 | 20,132.7           | 7,890         | "The non-HPC portion of the server market was                                                    |

| 4    | RIKEN Advanced<br>Institute for<br>Computational<br>Science (AICS)<br>Japan | K computer, SPARC64 VIIIfx<br>2.06Hz, Tofu interconnect<br>Fujitsu                                                                | 705,024   | 10,510.0 | 11,280.4           | 12,660        | actually down 20.5 per cent, to \$34.6bn"                                                        |

| 5    | DOE/SC/Argonne<br>National Laboratory<br>United States                      | Mira - BlueGene/Q, Power BQC<br>16C 1.60GHz, Custom<br>IBM                                                                        | 786,432   | 8,586.6  | 10,066.3           | 3,945         |                                                                                                  |

| 6    | Swiss National<br>Supercomputing<br>Centre (CSCS)<br>Switzerland            | Piz Daint - Cray XC30, Xeon E5-<br>2670 8C 2.600GHz, Aries<br>interconnect, NVIDIA K20x<br>Cray Inc.                              | 115,984   | 6,271.0  | 7,788.9            | 2,325         |                                                                                                  |

| 7    | Texas Advanced<br>Computing<br>Center/Univ. of Texas<br>United States       | Stampede - PowerEdge C8220,<br>Xeon E5-2680 8C 2.700GHz,<br>Infiniband FDR, Intel Xeon Phi<br>SE10P<br>Dell                       | 462,462   | 5,168.1  | 8,520.1            | 4,510         | www.top500.org                                                                                   |

| ETH zürich | n<br>→ Part spelinfethz.ch<br>y @spel_eth                                                                                                                                                                                                   |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Cas        | Case study: OS for High-Performance Computing                                                                                                                                                                                               |  |  |  |  |

|            | Remember the OS design goals?<br>What if performance is #1?                                                                                                                                                                                 |  |  |  |  |

|            | <ul> <li>Different environment</li> <li>Clusters, special architectures, datacenters</li> <li>Tens of thousands of nodes</li> <li>Hundreds of thousands of cores</li> <li>Millions of CHFs</li> <li>Unlimited fun <sup>(C)</sup></li> </ul> |  |  |  |  |

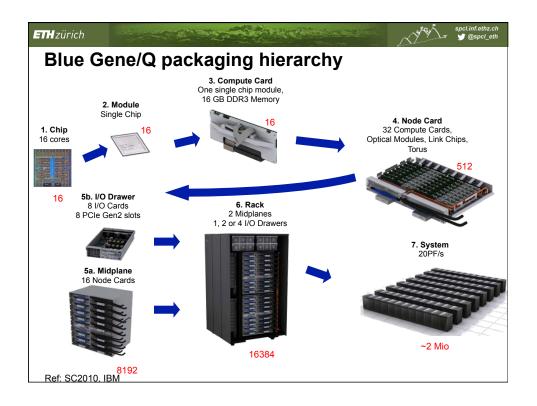

| BlueGene/Q Compute chip                  | <ul> <li>360 mm<sup>2</sup> Cu-45 technology (SOI)</li> <li>~ 1.47 B transistors</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PU P | <ul> <li>16 user + 1 service processors         <ul> <li>plus 1 redundant processor</li> <li>all processors are symmetric</li> <li>each 4-way multi-threaded</li> <li>64 bits PowerISA™</li> <li>1.6 GHz</li> <li>L1 I/D cache = 16kB/16kB</li> <li>L1 prefetch engines</li> <li>each processor has Quad FPU (4-wide double precision, SIMD)</li> </ul> </li> <li>peak performance 204.8 GFLOPS@55W</li> <li>Central shared L2 cache: 32 MB         <ul> <li>eDRAM</li> <li>multiversioned cache will support transactional memory, speculative execution.</li> <li>supports atomic ops</li> </ul> </li> <li>Dual memory controller         <ul> <li>16 GB external DDR3 memory</li> <li>1.33 Gb/s</li> <li>2 * 16 byte-wide interface (+ECC)</li> </ul> </li> </ul> |

| <b>ETH</b> zürich                                                                     | spcl.int.ethz.ch<br>y @spcl_eth                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Compute Node Kernel (CNK)                                                             |                                                                                                                                                                                                                                                                         |  |  |  |  |

| <ul> <li>stay</li> <li>Perfo<br/>partit</li> <li>Creation</li> <li>Loadion</li> </ul> | ates address space for execution of compute process(es)<br>ds code and initialized data for the executable                                                                                                                                                              |  |  |  |  |

| <ul> <li>Mem</li> <li>Add</li> </ul>                                                  | isfers processor control to the loaded executable<br>ory management<br>ress spaces are flat and fixed (no paging), and fit statically into PowerPC<br>TLBs                                                                                                              |  |  |  |  |

| <ul> <li>Proce</li> <li>The</li> <li>Time</li> </ul>                                  | rocess scheduling: only one thread per processor<br>essor control stays within the application, unless:<br>application issues a system call<br>er interrupt is received (requested by the application code)<br>abnormal event is detected, requiring kernel's attention |  |  |  |  |

| ETHzürich                                                                                  |                                                                        | spcl.inf.ethz.ch<br>y @spcl_eth |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------|

| iWAR                                                                                       | P and RoCE                                                             |                                 |

| <ul> <li>Ups<br/>Rot<br/>East</li> <li>Dov<br/>Hig<br/>Hig<br/>TC</li> <li>RoCI</li> </ul> | utable with existing infrastructure<br>sily portable (filtering, etc.) |                                 |

| ETHzürich                                                                                                                                                                                                                                         | - State - Contraction | spcl.inf.ethz.ch |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|

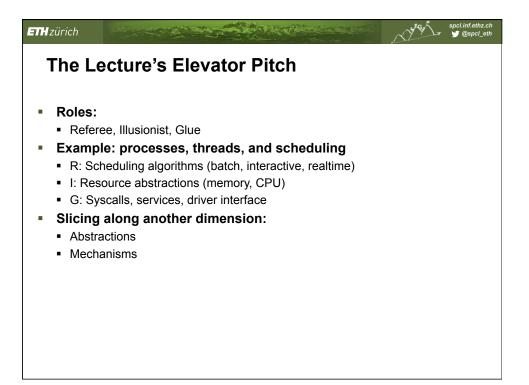

| The Lecture's Eleva                                                                                                                                                                                                                               | ator Pitch            |                  |

| <ul> <li>IPC and other communi</li> <li>A: Sockets, channels, rea</li> <li>M: Network devices, pack</li> </ul>                                                                                                                                    | d/write               |                  |

| <ul> <li>Memory Protection         <ul> <li>A: Access control</li> <li>M: Paging, protection ring</li> </ul> </li> <li>Paging/Segmentation         <ul> <li>A: Infinite memory, perform</li> <li>M: Caching, TLB, replaced</li> </ul> </li> </ul> | mance                 |                  |

|                                                                                                                                                                                                                                                   |                       |                  |

|                                                                                                                                                                                                                                                   |                       |                  |

| <b>ETH</b> zürid | ch                                                                                                                                                                                                                                                                                                                                                                                                 | North - | spcl.inf.ethz.ch<br>Ƴ @spcl_eth |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------|--|--|--|

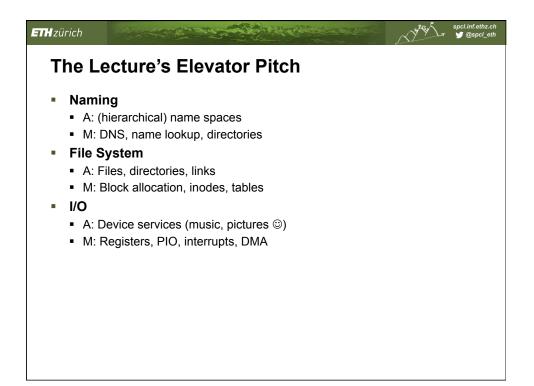

| Th               | The Lecture's Elevator Pitch                                                                                                                                                                                                                                                                                                                                                                       |         |                                 |  |  |  |

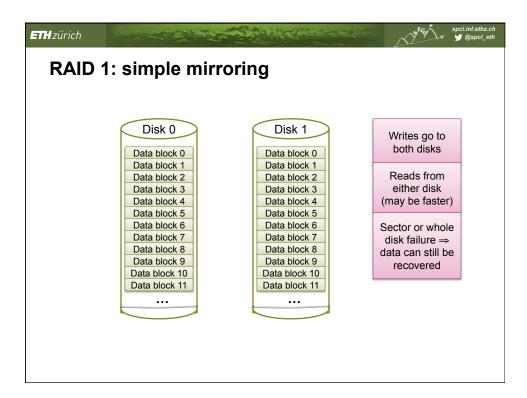

| - 4              | Reliability:         A: reliable hardware (storage)         M: Checksums, transactions, raid 0/5         And everything can be virtualized!         CPU, MMU, memory, devices, network         A: virtualized x86 CPU         M: paravirtualization, rewriting, hardware extensions         A: virtualized memory protection/management         M: writable pages, shadow pages, hw support, IOMMU |         |                                 |  |  |  |